指令級并行(Instruction-Level Parallelism, ILP)是現代計算機體系結構設計的核心概念之一,它旨在通過硬件技術提高程序的執行效率,使多條指令能夠在同一時間段內并行執行,從而提升處理器的性能。本章將聚焦于硬件方法,探討計算機體系結構如何通過硬件層面的設計來開發和利用指令級并行。

1. 指令級并行的定義與重要性

指令級并行是指在一個程序中,多條指令之間不存在數據依賴或控制依賴,因而可以同時執行。硬件方法通過設計復雜的處理器微架構來識別和利用這種并行性,例如流水線技術、超標量架構和動態調度等。ILP的開發對于打破傳統順序執行瓶頸至關重要,尤其是在高性能計算和嵌入式系統中,它能夠顯著加速指令吞吐率,提升整體計算能力。

2. 硬件方法的核心技術

硬件方法開發ILP主要包括以下幾個方面:

- 流水線技術:將指令執行過程劃分為多個階段(如取指、譯碼、執行、訪存、寫回),使不同指令在不同階段重疊執行,從而提高吞吐率。但流水線可能面臨結構冒險、數據冒險和控制冒險等問題,需要硬件機制(如旁路、分支預測)來解決。

- 超標量架構:處理器在每個時鐘周期內可以發射并執行多條指令,通過硬件動態調度指令順序,以最大化并行性。超標量處理器通常包含多個功能單元(如ALU、FPU),能夠同時處理不同類型的指令。

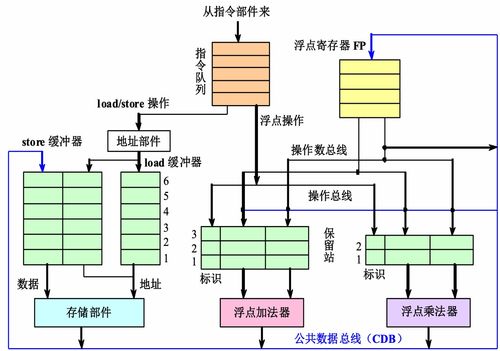

- 動態調度與亂序執行:硬件通過重排序緩沖區(ROB)和保留站(Reservation Station)等機制,動態檢測指令依賴關系,將無依賴的指令提前執行,以隱藏延遲并提高資源利用率。

- 分支預測技術:為了減少控制冒險帶來的流水線停頓,硬件采用分支預測器(如靜態預測、動態預測)來預測分支指令的走向,確保指令流的連續性。

- 寄存器重命名:通過硬件映射邏輯寄存器到物理寄存器,消除寫后寫(WAW)和寫后讀(WAR)假依賴,增加指令并行執行的機會。

3. 硬件方法的優勢與挑戰

硬件方法開發ILP具有顯著優勢:它無需修改軟件代碼,通過透明化的硬件優化即可提升性能;能夠適應動態的程序行為,實時調整指令調度。硬件方法也面臨挑戰:復雜的硬件設計會增加芯片面積、功耗和成本;并行性的挖掘受限于指令間的固有依賴,可能遭遇收益遞減;硬件錯誤(如分支預測失敗)可能導致性能下降。

4. 實際應用與未來發展

在實際計算機系統中,硬件方法已廣泛應用于現代處理器,如Intel的Core系列和ARM的Cortex系列。這些處理器結合了多種ILP技術,以實現高性能和能效平衡。隨著人工智能和物聯網的發展,硬件方法將繼續演進,例如通過更智能的預測算法、異構計算架構以及近似計算技術,來應對日益復雜的計算需求。

硬件方法是開發指令級并行的關鍵途徑,它通過創新的微架構設計,推動了計算機性能的持續提升。理解這些技術不僅有助于優化處理器設計,也為軟件開發提供了底層性能洞察,是計算機體系結構學習中不可或缺的一環。